4 bit ALU-Verilog Code

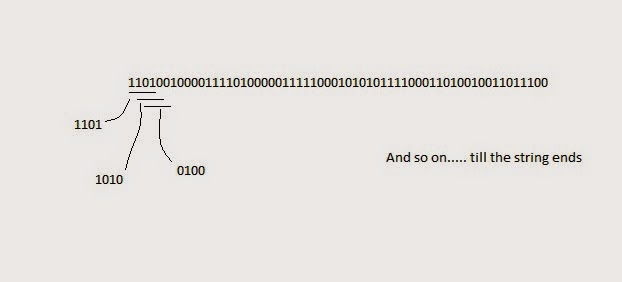

Hi Friends, I come up with a new post on 4 bit ALU using Verilog. It has both Structural as well as Behavioral models. This code was made by me and my friend Maunil. Our ALU has Following Components:- 1).Comparator 2).Adder/Subtractor 3).Shifter(Right/Right-Arithmetic/Left) 4).Logical Block Previously I posted an article on building 32 bit ALU in Logisim(Structural Model) This was written in verilog in Xilinx Platform and tested on Basys 2 FPGA(you may be knowing this thing and how to load our verilog code in this) So, below is the link for that code in the notepad you can make it verilog file by changing it extension to .v from .txt(You may also be knowing this. Link:- https://drive.google.com/file/d/0B36eSzxwoMyUTmRlSGxYa0RnRUk/view?usp=sharing Below is the link to .ucf file(contains the connections for basys 2 to test the code in that device) after downloading change its extension to .ucf from .txt. Link:- https://drive.google.com/file/d/0B36eSzxwoMyUcDd5V...